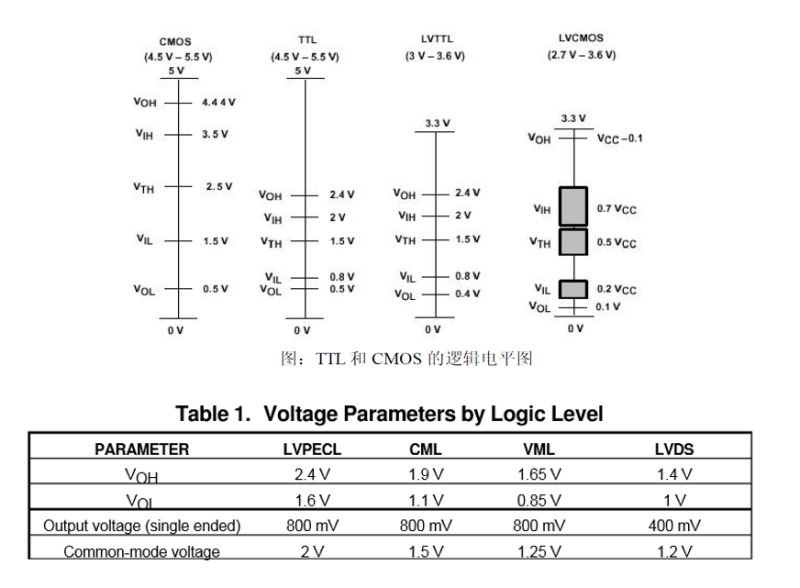

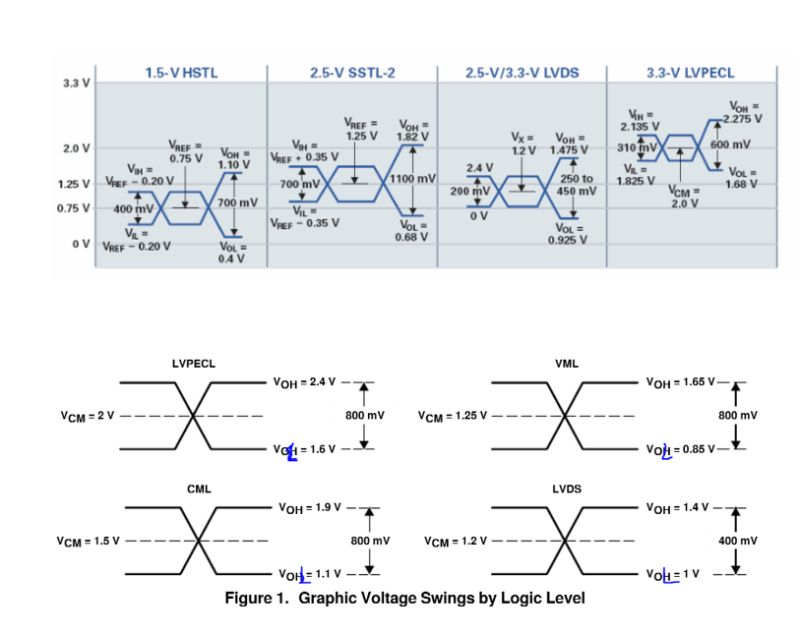

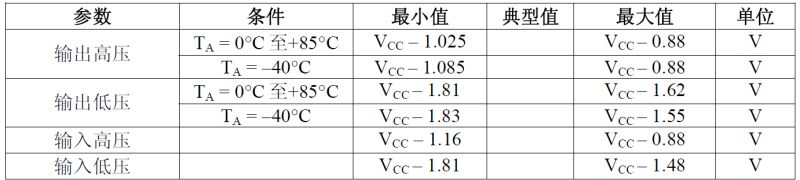

In diesem Artikel werden hauptsächlich die gängigen Logikebenenstandards wie CMOS, LVCMOS, TTL, LVTTL, LVDS, PECL / LVPECL, CML, VML, HSTL, SSTL usw. vorgestellt.

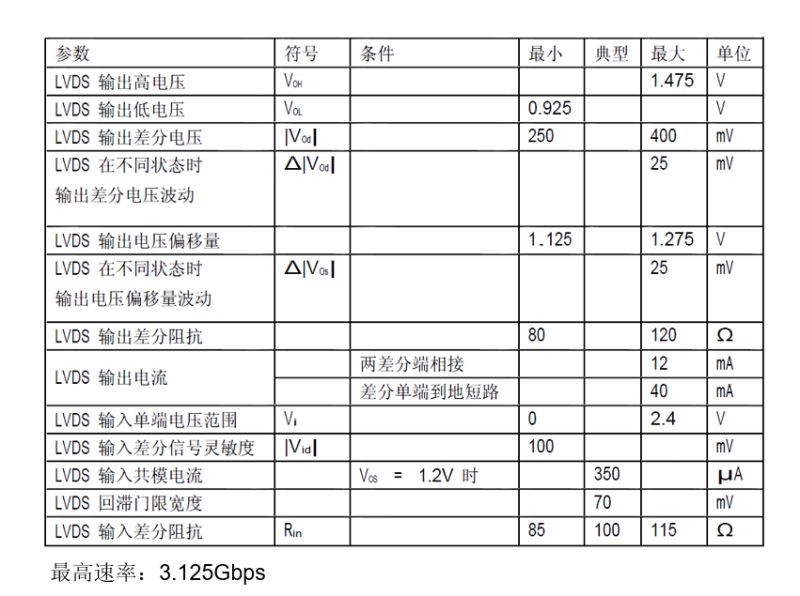

LVPECL:

Höchste Rate: LVPECL beträgt 10 + Gbit/s

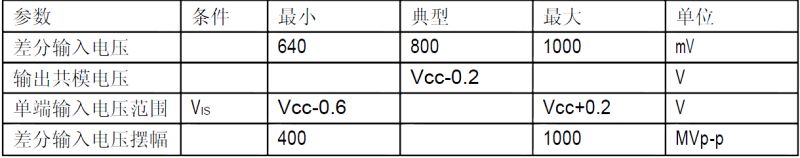

CML:

Maximale Rate: 10 + Gbit/s

Kopplungsmodus: Eine Gleichstromkopplung wird zwischen CML und CML verwendet, wenn der VCC gleich ist, und eine Wechselstromkopplung wird zwischen CML und CML verwendet, wenn der VCC unterschiedlich ist

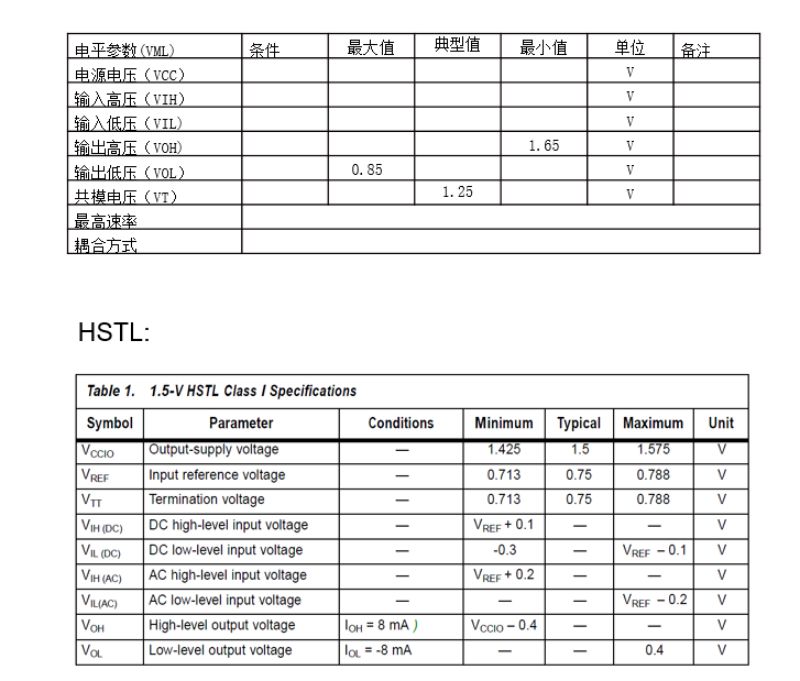

Elektrische SSTL-Ebene

Der Standard ist speziell für Hochgeschwindigkeitsspeicherschnittstellen (insbesondere SDRAM) gedacht, die mit bis zu 200 MHz arbeiten, und SSTL wird hauptsächlich in DDR-Speichern verwendet. Und das Gleiche wie HSTL. VCCIO = 2,5 V. Der Eingang ist eine Komparatorstruktur mit einem Referenzpegel von 1,25 V an einem Ende und einem Eingangssignal am anderen Ende. Die Anforderungen an den Referenzpegel sind relativ hoch (1 % Genauigkeit), HSTL und SSTL werden meist unter 300 MB verwendet.

Das Obige ist die Einführung gemeinsamer Logikpegelstandards, die von Shenzhen HDV Phoelectron Technology Co., LTD eingeführt wurden. Unsere verwandte optische Modulserie umfasst: optisches SFP-Modul, optisches SFF-Modul, optisches Kommunikationsmodul, optisches 1x9-Modul, optisches Modul für Kommunikationsgeräte, bidirektionales optisches Doppelfasermodul und so weiter. Wenn Sie weitere Arten von Modulanforderungen haben, konsultieren Sie bitte weiter unten.