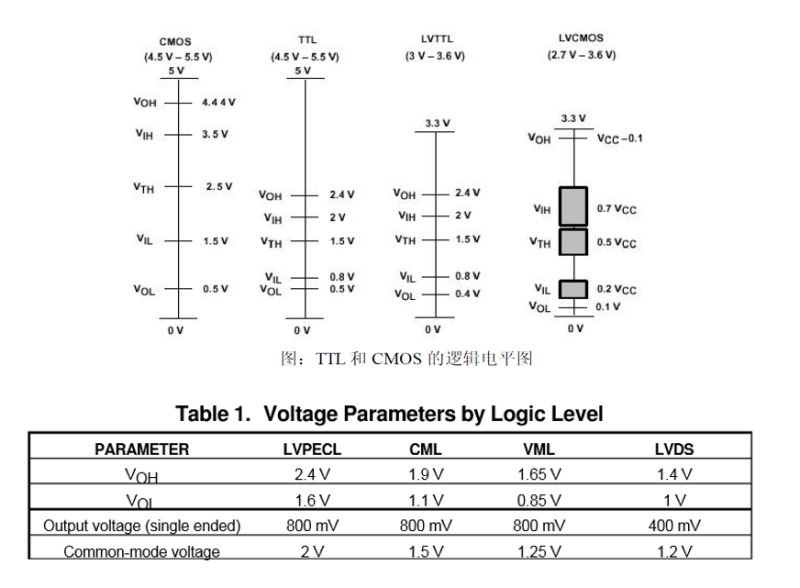

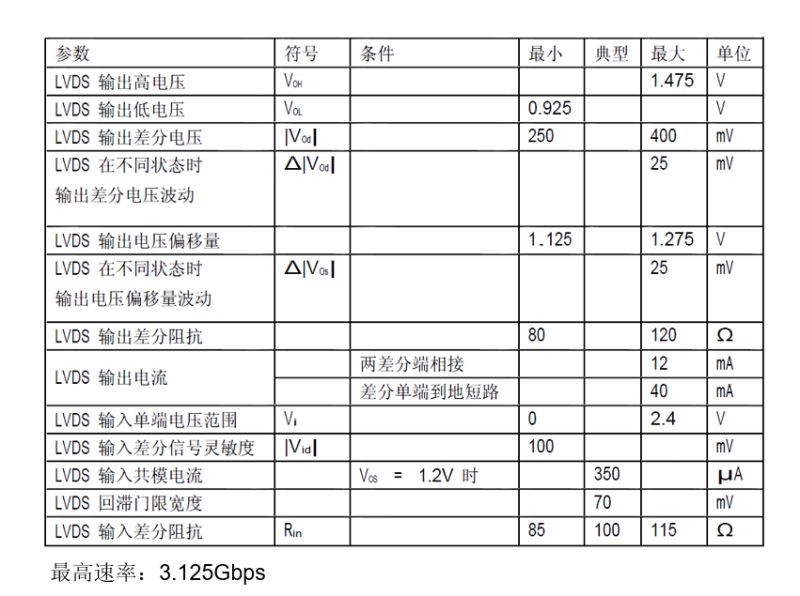

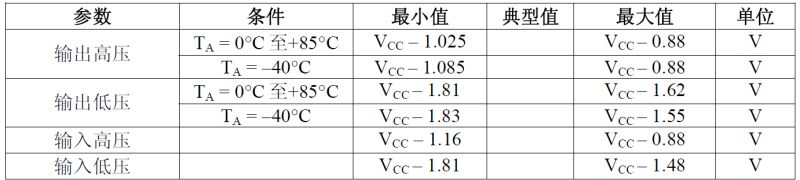

Artikel ini terutamanya memperkenalkan piawaian tahap logik biasa, seperti CMOS, LVCMOS, TTL, LVTTL, LVDS, PECL / LVPECL, CML, VML, HSTL, SSTL, dsb.

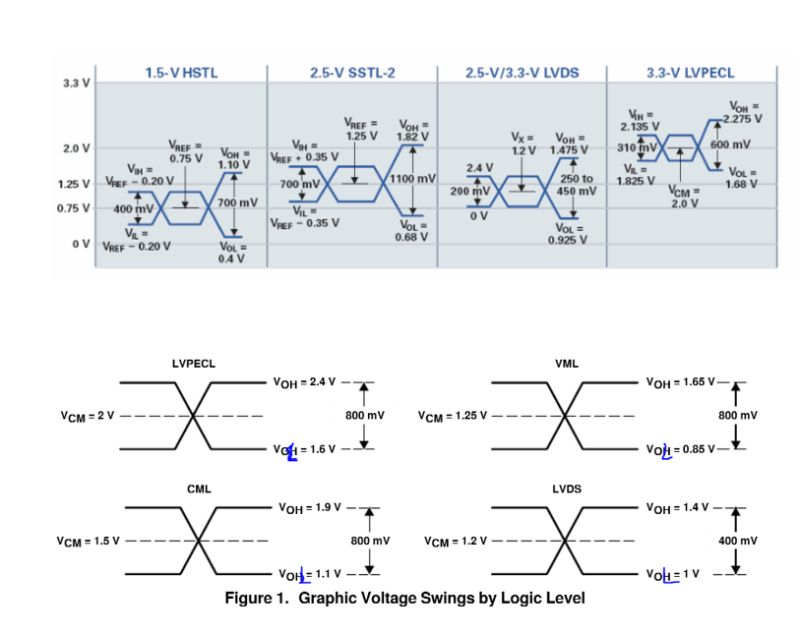

LVPECL:

Kadar tertinggi: LVPECL ialah 10 + Gbps

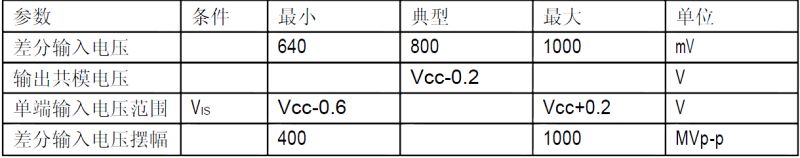

CML:

Kadar maksimum: 10 + Gbps

Mod gandingan:Gandingan Dc digunakan antara CML dan CML apabila VCC adalah sama, dan gandingan AC digunakan antara CML dan CML apabila VCC berbeza

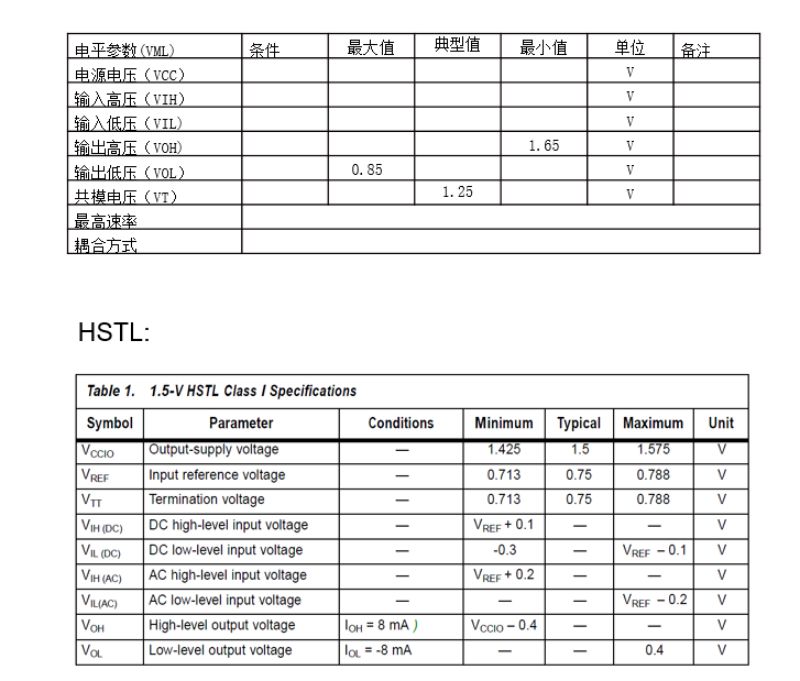

Tahap elektrik SSTL

Standard ini khusus untuk antara muka memori berkelajuan tinggi (terutamanya SDRAM), yang berfungsi sehingga 200 MHz, dan SSTL digunakan terutamanya dalam memori DDR. Dan sama seperti HSTL. V¬¬CCIO=2.5V, Input ialah struktur pembanding dengan tahap rujukan 1.25V pada satu hujung dan isyarat input pada hujung yang lain. Keperluan tahap rujukan agak tinggi (ketepatan 1%), HSTL dan SSTL kebanyakannya digunakan di bawah 300M.

Di atas ialah pengenalan piawaian tahap logik biasa yang dibawa oleh Shenzhen HDV Phoelectron Technology Co., LTD. Siri modul optik berkaitan kami termasuk: modul optik SFP, modul optik SFF, modul optik komunikasi, modul optik 1x9, modul optik peralatan komunikasi, modul optik dwiarah gentian dwi dan sebagainya. Jika anda mempunyai lebih banyak jenis keperluan modul, sila rujuk lebih lanjut.