EPON সিস্টেমে, OLT একটি POS (প্যাসিভ অপটিক্যাল স্প্লিটার) এর মাধ্যমে একাধিক ONUs (অপটিক্যাল নেটওয়ার্ক ইউনিট) এর সাথে সংযুক্ত থাকে।EPON এর মূল হিসাবে, OLT অপটিক্যাল মডিউলগুলি সরাসরি সমগ্র 10G EPON সিস্টেমের অপারেশনকে প্রভাবিত করবে।

1.10G EPON সিমেট্রিকাল OLT অপটিক্যাল মডিউলের ভূমিকা

10G EPON সিমেট্রিকাল OLT অপটিক্যাল মডিউল আপলিংক বার্স্ট রিসেপশন এবং ডাউনলিংক একটানা ট্রান্সমিশন মোড ব্যবহার করে, যা মূলত 10G EPON সিস্টেমে অপটিক্যাল/ইলেক্ট্রিক্যাল রূপান্তরের জন্য ব্যবহৃত হয়।

প্রাপ্ত অংশে রয়েছে একটি TIA (ট্রান্সিম্পেড্যান্স এমপ্লিফায়ার), একটি APD (অ্যাভাল্যাঞ্চ ফটোডিওড) 1270/1310nm, এবং দুটি LA (সীমাবদ্ধ পরিবর্ধক) 1.25 এবং 10.3125 Gbit/s হারে।

ট্রান্সমিটিং প্রান্তটি একটি 10G EML (ইলেক্ট্রো-শোষণ মডুলেশন লেজার) এবং একটি 1.25 Gbit/s DFB (ডিস্ট্রিবিউটেড ফিডব্যাক লেজার) দ্বারা গঠিত এবং এর নির্গমন তরঙ্গদৈর্ঘ্য যথাক্রমে 1577 এবং 1490nm।

ড্রাইভিং সার্কিটে একটি স্থিতিশীল 10G লেজার নির্গমন তরঙ্গদৈর্ঘ্য বজায় রাখার জন্য একটি ডিজিটাল APC (স্বয়ংক্রিয় অপটিক্যাল পাওয়ার কন্ট্রোল) সার্কিট এবং একটি TEC (তাপমাত্রা ক্ষতিপূরণ) সার্কিট অন্তর্ভুক্ত রয়েছে।SFF-8077iv4.5 প্রোটোকল অনুযায়ী একক চিপ মাইক্রোকম্পিউটার দ্বারা ট্রান্সমিটিং এবং রিসিভিং প্যারামিটার পর্যবেক্ষণ করা হয়।

যেহেতু OLT অপটিক্যাল মডিউলের রিসিভিং এন্ড বার্স্ট রিসেপশন ব্যবহার করে, অভ্যর্থনা সেটআপ সময় বিশেষভাবে গুরুত্বপূর্ণ।অভ্যর্থনা নিষ্পত্তির সময় দীর্ঘ হলে, এটি সংবেদনশীলতাকে ব্যাপকভাবে প্রভাবিত করবে এবং এমনকি বিস্ফোরিত অভ্যর্থনাটি সঠিকভাবে কাজ না করার কারণ হতে পারে।IEEE 802.3av প্রোটোকলের প্রয়োজনীয়তা অনুসারে, একটি 1.25Gbit/s বার্স্ট রিসেপশনের প্রতিষ্ঠার সময় অবশ্যই <400 ns হতে হবে, এবং বার্স্ট অভ্যর্থনা সংবেদনশীলতা হতে হবে <-29.78 dBm বিট ত্রুটির হার 10-12;এবং 10.3125 Gbit/s বিস্ফোরিত অভ্যর্থনা সেটআপ সময় অবশ্যই <800ns হতে হবে, এবং বার্স্ট অভ্যর্থনা সংবেদনশীলতা অবশ্যই <-28.0 dBm হতে হবে বিট ত্রুটির হার 10-3।

2.10G EPON সিমেট্রিকাল OLT অপটিক্যাল মডিউল ডিজাইন

2.1 ডিজাইন স্কিম

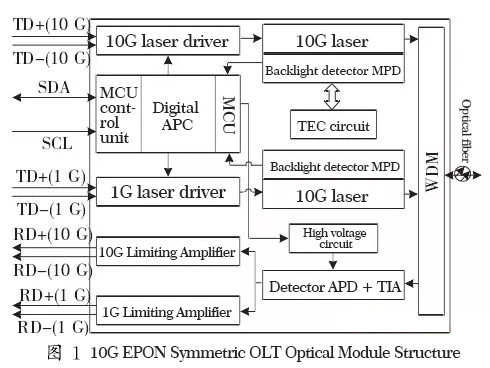

10G EPON সিমেট্রিকাল OLT অপটিক্যাল মডিউলটি একটি ট্রিপলেক্সার (একক-ফাইবার থ্রি-ওয়ে মডিউল), ট্রান্সমিটিং, গ্রহণ এবং পর্যবেক্ষণের সমন্বয়ে গঠিত।ট্রিপলেক্সারটিতে দুটি লেজার এবং একটি ডিটেক্টর রয়েছে।প্রেরিত আলো এবং প্রাপ্ত আলো একক-ফাইবার দ্বিমুখী সংক্রমণ অর্জনের জন্য WDM (তরঙ্গদৈর্ঘ্য বিভাগ মাল্টিপ্লেক্সার) এর মাধ্যমে অপটিক্যাল ডিভাইসে একত্রিত হয়।এর গঠন চিত্র 1 এ দেখানো হয়েছে।

ট্রান্সমিটিং অংশে দুটি লেজার রয়েছে, যার প্রধান কাজ হল যথাক্রমে 1G এবং 10G বৈদ্যুতিক সংকেতগুলিকে অপটিক্যাল সিগন্যালে রূপান্তর করা এবং একটি ডিজিটাল APC সার্কিটের মাধ্যমে একটি বন্ধ লুপ অবস্থায় অপটিক্যাল পাওয়ার স্থিতিশীলতা বজায় রাখা।একই সময়ে, একক-চিপ মাইক্রোকম্পিউটার সিস্টেমের জন্য প্রয়োজনীয় বিলুপ্তি অনুপাত পেতে মডুলেশন কারেন্টের মাত্রা নিয়ন্ত্রণ করে।TEC সার্কিটটি 10G ট্রান্সমিটিং সার্কিটে যোগ করা হয়েছে, যা 10G লেজারের আউটপুট তরঙ্গদৈর্ঘ্যকে ব্যাপকভাবে স্থিতিশীল করে।প্রাপ্ত অংশটি সনাক্ত করা বিস্ফোরিত অপটিক্যাল সিগন্যালকে বৈদ্যুতিক সংকেতে রূপান্তর করতে APD ব্যবহার করে এবং পরিবর্ধন এবং আকার দেওয়ার পরে এটিকে আউটপুট করে।সংবেদনশীলতা আদর্শ পরিসরে পৌঁছাতে পারে তা নিশ্চিত করার জন্য, বিভিন্ন তাপমাত্রায় APD-কে একটি স্থিতিশীল উচ্চ চাপ প্রদান করা প্রয়োজন।এক-চিপ কম্পিউটার APD উচ্চ-ভোল্টেজ সার্কিট নিয়ন্ত্রণ করে এই লক্ষ্য অর্জন করে।

2.2 ডুয়াল-রেট বার্স্ট রিসেপশন বাস্তবায়ন

10G EPON সিমেট্রিক OLT অপটিক্যাল মডিউলের প্রাপ্ত অংশটি একটি বিস্ফোরিত গ্রহণ পদ্ধতি ব্যবহার করে।এটিকে 1.25 এবং 10.3125 Gbit/s এর দুটি ভিন্ন হারের বিস্ফোরণ সংকেত গ্রহণ করতে হবে, যার জন্য স্থিতিশীল আউটপুট বৈদ্যুতিক সংকেত পেতে এই দুটি ভিন্ন হারের অপটিক্যাল সংকেতগুলিকে ভালভাবে আলাদা করতে সক্ষম হওয়া প্রয়োজন।OLT অপটিক্যাল মডিউলের ডুয়াল-রেট বার্স্ট রিসেপশন বাস্তবায়নের জন্য দুটি স্কিম এখানে প্রস্তাব করা হয়েছে।

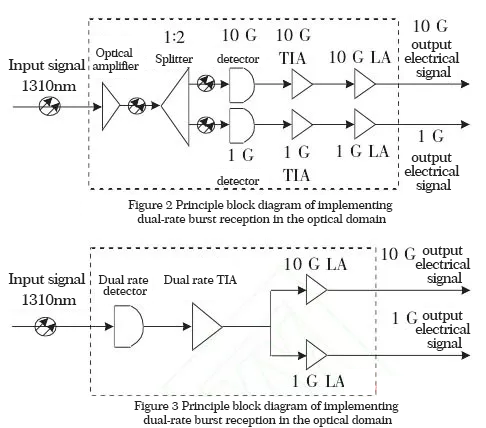

যেহেতু ইনপুট অপটিক্যাল সিগন্যাল টিডিএমএ (টাইম ডিভিশন মাল্টিপল অ্যাক্সেস) প্রযুক্তি ব্যবহার করে, একই সময়ে শুধুমাত্র একটি বিস্ফোরিত আলোর হার থাকতে পারে।ইনপুট সিগন্যালকে অপটিক্যাল ডোমেনে 1:2 অপটিক্যাল স্প্লিটারের মাধ্যমে আলাদা করা যেতে পারে, যেমন চিত্র 2-এ দেখানো হয়েছে। অথবা 1G এবং 10G অপটিক্যাল সিগন্যালকে দুর্বল বৈদ্যুতিক সংকেতে রূপান্তর করতে শুধুমাত্র একটি উচ্চ-গতির ডিটেক্টর ব্যবহার করুন এবং তারপরে দুটি বৈদ্যুতিক সংকেতকে আলাদা করুন। একটি বৃহত্তর ব্যান্ডউইথ TIA এর মাধ্যমে বিভিন্ন হারের সংকেত, যেমন চিত্র 3 এ দেখানো হয়েছে।

চিত্র 2-এ দেখানো প্রথম স্কিমটি 1:2 অপটিক্যাল স্প্লিটারের মধ্য দিয়ে যাওয়ার সময় একটি নির্দিষ্ট সন্নিবেশ ক্ষতি আনবে, যা ইনপুট অপটিক্যাল সিগন্যালকে প্রশস্ত করতে হবে, তাই অপটিক্যাল স্প্লিটারের সামনে একটি অপটিক্যাল পরিবর্ধক ইনস্টল করা আছে।বিচ্ছিন্ন অপটিক্যাল সিগন্যালগুলি তারপর বিভিন্ন হারের ডিটেক্টর দ্বারা অপটিক্যাল/ইলেক্ট্রিক্যাল রূপান্তর সাপেক্ষে এবং অবশেষে দুটি ধরণের স্থিতিশীল বৈদ্যুতিক সংকেত আউটপুট পাওয়া যায়।এই সমাধানের সবচেয়ে বড় অসুবিধা হল একটি অপটিক্যাল এমপ্লিফায়ার এবং একটি 1:2 অপটিক্যাল স্প্লিটার ব্যবহার করা হয় এবং অপটিক্যাল সিগন্যালকে রূপান্তর করার জন্য দুটি ডিটেক্টর প্রয়োজন, যা বাস্তবায়নের জটিলতা বাড়ায় এবং খরচ বাড়ায়।

দ্বিতীয় স্কিমে FIG দেখানো হয়েছে.3, বৈদ্যুতিক ডোমেনে বিচ্ছেদ অর্জনের জন্য ইনপুট অপটিক্যাল সিগন্যালকে শুধুমাত্র একটি ডিটেক্টর এবং একটি TIA এর মধ্য দিয়ে যেতে হবে।এই সমাধানের মূল বিষয় টিআইএ নির্বাচনের মধ্যে রয়েছে, যার জন্য টিআইএ-এর 1 ~ 10Gbit/s ব্যান্ডউইথ থাকা প্রয়োজন এবং একই সময়ে এই ব্যান্ডউইথের মধ্যে TIA-এর দ্রুত প্রতিক্রিয়া রয়েছে।শুধুমাত্র TIA এর বর্তমান প্যারামিটারের মাধ্যমে দ্রুত প্রতিক্রিয়া মান পেতে পারে, প্রাপ্তির সংবেদনশীলতা ভালভাবে নিশ্চিত করা যেতে পারে।এই সমাধানটি বাস্তবায়নের জটিলতাকে ব্যাপকভাবে হ্রাস করে এবং খরচ নিয়ন্ত্রণে রাখে।প্রকৃত ডিজাইনে, আমরা সাধারণত ডুয়াল-রেট বার্স্ট রিসেপশন অর্জনের জন্য দ্বিতীয় স্কিমটি বেছে নিই।

2.3 রিসিভিং শেষে হার্ডওয়্যার সার্কিটের ডিজাইন

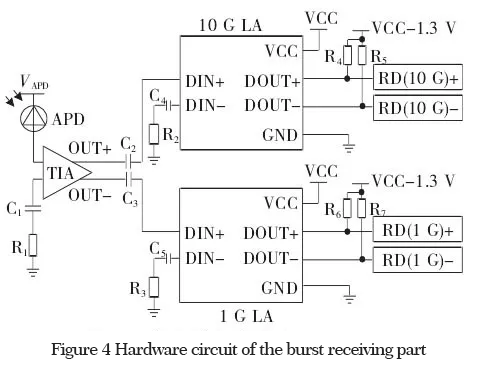

চিত্র 4 হল বার্স্ট রিসিভিং অংশের হার্ডওয়্যার সার্কিট।যখন একটি বিস্ফোরিত অপটিক্যাল ইনপুট থাকে, তখন APD অপটিক্যাল সংকেতকে একটি দুর্বল বৈদ্যুতিক সংকেতে রূপান্তর করে এবং এটি টিআইএ-তে পাঠায়।সংকেত টিআইএ দ্বারা একটি 10G বা 1G বৈদ্যুতিক সংকেতে পরিবর্ধিত হয়।10G বৈদ্যুতিক সংকেত টিআইএ-এর ইতিবাচক সংযোগের মাধ্যমে 10G LA-তে ইনপুট করা হয় এবং 1G বৈদ্যুতিক সংকেত টিআইএ-এর নেতিবাচক সংযোগের মাধ্যমে 1G LA-তে ইনপুট হয়।ক্যাপাসিটার C2 এবং C3 হল কাপলিং ক্যাপাসিটর যা 10G এবং 1G AC-কাপলড আউটপুট অর্জন করতে ব্যবহৃত হয়।এসি-কাপল্ড পদ্ধতিটি বেছে নেওয়া হয়েছিল কারণ এটি ডিসি-কাপল্ড পদ্ধতির চেয়ে সহজ।

যাইহোক, এসি কাপলিং-এ ক্যাপাসিটরের চার্জ এবং ডিসচার্জ থাকে এবং সিগন্যালের প্রতিক্রিয়া গতি চার্জ এবং ডিসচার্জ সময় ধ্রুবক দ্বারা প্রভাবিত হয়, অর্থাৎ, সিগন্যালে সময়মত সাড়া দেওয়া যায় না।এই বৈশিষ্ট্যটি একটি নির্দিষ্ট পরিমাণ অভ্যর্থনা নিষ্পত্তির সময় হারাতে বাধ্য, তাই এসি কাপলিং ক্যাপাসিটর কত বড় তা চয়ন করা গুরুত্বপূর্ণ।যদি একটি ছোট কাপলিং ক্যাপাসিটর নির্বাচন করা হয়, তাহলে নিষ্পত্তির সময় সংক্ষিপ্ত করা যেতে পারে, এবং প্রতিটি টাইম স্লটে ONU দ্বারা প্রেরিত সংকেত অভ্যর্থনা প্রভাবকে প্রভাবিত না করে সম্পূর্ণরূপে গ্রহণ করা যেতে পারে কারণ অভ্যর্থনা নিষ্পত্তির সময়টি খুব দীর্ঘ এবং পরবর্তী সময়ের আগমন। স্লট

যাইহোক, খুব ছোট ক্যাপাসিট্যান্স কাপলিং প্রভাবকে প্রভাবিত করবে এবং অভ্যর্থনার স্থায়িত্বকে ব্যাপকভাবে হ্রাস করবে।বৃহত্তর ক্যাপ্যাসিট্যান্স সিস্টেমের ঝাঁকুনি কমাতে পারে এবং প্রাপ্তির প্রান্তের সংবেদনশীলতা উন্নত করতে পারে।অতএব, অভ্যর্থনা নিষ্পত্তির সময় এবং অভ্যর্থনা সংবেদনশীলতা বিবেচনায় নেওয়ার জন্য, উপযুক্ত কাপলিং ক্যাপাসিটার C2 এবং C3 নির্বাচন করতে হবে।উপরন্তু, ইনপুট বৈদ্যুতিক সংকেতের স্থায়িত্ব নিশ্চিত করার জন্য, একটি কাপলিং ক্যাপাসিটর এবং 50Ω এর প্রতিরোধের সাথে একটি ম্যাচিং প্রতিরোধক LA এর নেতিবাচক টার্মিনালের সাথে সংযুক্ত করা হয়েছে।

LVPECL (লো ভোল্টেজ পজিটিভ ইমিটার কাপলিং লজিক) 10G (1G) LA দ্বারা ডিফারেনশিয়াল সিগন্যাল আউটপুটের মাধ্যমে প্রতিরোধক R4 এবং R5 (R6 এবং R7) এবং একটি 2.0 V DC ভোল্টেজ উৎস দ্বারা গঠিত সার্কিট।বৈদ্যুতিক সংকেত।

2.4 লঞ্চ বিভাগ

10G EPON সিমেট্রিক OLT অপটিক্যাল মডিউলের ট্রান্সমিটিং অংশটি প্রধানত 1.25 এবং 10G ট্রান্সমিটিং-এর দুটি অংশে বিভক্ত, যা যথাক্রমে ডাউনলিংকে 1490 এবং 1577 এনএম তরঙ্গদৈর্ঘ্য সহ সংকেত পাঠায়।একটি উদাহরণ হিসাবে 10G ট্রান্সমিটিং অংশটিকে নিলে, 10G ডিফারেনশিয়াল সিগন্যালের একটি জোড়া একটি CDR (ক্লক শেপিং) চিপে প্রবেশ করে, একটি 10G ড্রাইভার চিপের সাথে AC-কাপল করা হয় এবং অবশেষে একটি 10G লেজারে আলাদাভাবে ইনপুট করা হয়।কারণ তাপমাত্রা পরিবর্তন লেজার নির্গমন তরঙ্গদৈর্ঘ্যের উপর একটি বড় প্রভাব ফেলবে, প্রোটোকল দ্বারা প্রয়োজনীয় স্তরে তরঙ্গদৈর্ঘ্যকে স্থিতিশীল করার জন্য (প্রটোকলের জন্য 1575 ~ 1580nm প্রয়োজন), TEC সার্কিটের কার্যকারী বর্তমানকে সামঞ্জস্য করতে হবে, তাই যে আউটপুট তরঙ্গদৈর্ঘ্য ভাল নিয়ন্ত্রণ করা যেতে পারে.

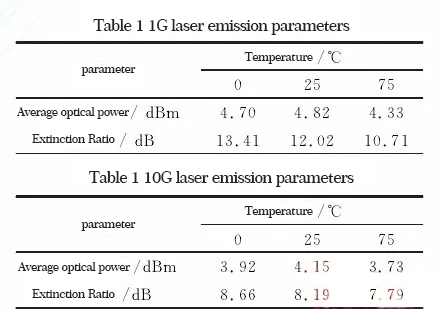

3. পরীক্ষার ফলাফল এবং বিশ্লেষণ

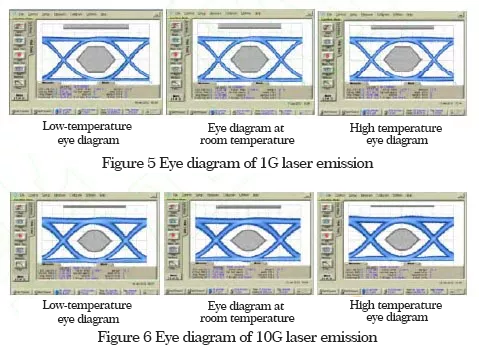

10G EPON সিমেট্রিক OLT অপটিক্যাল মডিউলের প্রধান পরীক্ষার সূচকগুলির মধ্যে রয়েছে রিসিভার সেটআপের সময়, রিসিভারের সংবেদনশীলতা এবং ট্রান্সমিট আই ডায়াগ্রাম।নির্দিষ্ট পরীক্ষা নিম্নরূপ:

(1) সেটআপ সময় গ্রহণ করুন

আপলিংক বার্স্ট অপটিক্যাল পাওয়ার-24.0 dBm-এর স্বাভাবিক কাজের পরিবেশের অধীনে, বার্স্ট লাইট সোর্স দ্বারা নির্গত অপটিক্যাল সিগন্যাল পরিমাপের সূচনা পয়েন্ট হিসাবে ব্যবহৃত হয় এবং মডিউল পরিমাপের শেষ বিন্দু হিসাবে একটি সম্পূর্ণ বৈদ্যুতিক সংকেত গ্রহণ করে এবং স্থাপন করে, উপেক্ষা করে পরীক্ষার ফাইবারে আলোর সময় বিলম্ব। পরিমাপ করা 1G বার্স্ট রিসেপশন সেটআপের সময় হল 76.7 এনএস, যা <400 এনএস-এর আন্তর্জাতিক মান পূরণ করে;10G বার্স্ট রিসেপশন সেটআপের সময় হল 241.8 ns, যা <800 ns এর আন্তর্জাতিক মানও পূরণ করে৷

3. পরীক্ষার ফলাফল এবং বিশ্লেষণ

10G EPON সিমেট্রিক OLT অপটিক্যাল মডিউলের প্রধান পরীক্ষার সূচকগুলির মধ্যে রয়েছে রিসিভার সেটআপের সময়, রিসিভারের সংবেদনশীলতা এবং ট্রান্সমিট আই ডায়াগ্রাম।নির্দিষ্ট পরীক্ষা নিম্নরূপ:

(1) সেটআপ সময় গ্রহণ করুন

আপলিংক বার্স্ট অপটিক্যাল পাওয়ার-24.0 dBm-এর স্বাভাবিক কাজের পরিবেশের অধীনে, বার্স্ট লাইট সোর্স দ্বারা নির্গত অপটিক্যাল সিগন্যাল পরিমাপের সূচনা পয়েন্ট হিসাবে ব্যবহৃত হয় এবং মডিউল পরিমাপের শেষ বিন্দু হিসাবে একটি সম্পূর্ণ বৈদ্যুতিক সংকেত গ্রহণ করে এবং স্থাপন করে, উপেক্ষা করে পরীক্ষার ফাইবার আলোর সময় বিলম্ব.পরিমাপকৃত 1G বার্স্ট রিসেপশন সেটআপের সময় হল 76.7 ns, যা <400 ns-এর আন্তর্জাতিক মান পূরণ করে;10G বার্স্ট রিসেপশন সেটআপের সময় হল 241.8 ns, যা <800 ns এর আন্তর্জাতিক মানও পূরণ করে৷