EPON प्रणालीमध्ये, OLT हे POS (पॅसिव्ह ऑप्टिकल स्प्लिटर) द्वारे एकाधिक ONUs (ऑप्टिकल नेटवर्क युनिट्स) शी जोडलेले आहे.EPON चा मुख्य भाग म्हणून, OLT ऑप्टिकल मॉड्यूल संपूर्ण 10G EPON प्रणालीच्या ऑपरेशनवर थेट परिणाम करतील.

1. 10G EPON सममितीय OLT ऑप्टिकल मॉड्यूलचा परिचय

10G EPON सममितीय OLT ऑप्टिकल मॉड्यूल अपलिंक बर्स्ट रिसेप्शन आणि डाउनलिंक सतत ट्रांसमिशन मोड वापरते, जे मुख्यतः 10G EPON प्रणालींमध्ये ऑप्टिकल/इलेक्ट्रिकल रूपांतरणासाठी वापरले जातात.

प्राप्त भागामध्ये 1.25 आणि 10.3125 Gbit/s दरांवर TIA (ट्रान्सिम्पेडन्स अॅम्प्लीफायर), 1270 / 1310nm वर एक APD (अव्हलांच फोटोडिओड) आणि दोन LA (मर्यादित अॅम्प्लीफायर) असतात.

ट्रान्समिटिंग एंड 10G EML (इलेक्ट्रो-अॅब्सॉर्प्शन मॉड्युलेशन लेसर) आणि 1.25 Gbit/s DFB (वितरित फीडबॅक लेसर) ने बनलेला आहे आणि त्याची उत्सर्जन तरंगलांबी अनुक्रमे 1577 आणि 1490nm आहे.

ड्रायव्हिंग सर्किटमध्ये स्थिर 10G लेसर उत्सर्जन तरंगलांबी राखण्यासाठी डिजिटल APC (ऑटोमॅटिक ऑप्टिकल पॉवर कंट्रोल) सर्किट आणि TEC (तापमान भरपाई) सर्किट समाविष्ट आहे.SFF-8077iv4.5 प्रोटोकॉलनुसार प्रसारित करणे आणि प्राप्त करणे पॅरामीटर मॉनिटरिंग सिंगल चिप मायक्रोकॉम्प्यूटरद्वारे लागू केले जाते.

कारण OLT ऑप्टिकल मॉड्युलचा रिसीव्हिंग एंड बर्स्ट रिसेप्शन वापरतो, रिसेप्शन सेटअप वेळ विशेषतः महत्वाचा आहे.रिसेप्शन सेटलमेंटची वेळ जास्त असल्यास, त्याचा संवेदनशीलतेवर मोठ्या प्रमाणात परिणाम होतो आणि त्यामुळे बर्स्ट रिसेप्शन योग्यरित्या कार्य करू शकत नाही.IEEE 802.3av प्रोटोकॉलच्या आवश्यकतांनुसार, 1.25Gbit/s बर्स्ट रिसेप्शनची स्थापना वेळ <400 ns असणे आवश्यक आहे आणि 10-12 च्या बिट त्रुटी दरासह बर्स्ट रिसेप्शन संवेदनशीलता <-29.78 dBm असणे आवश्यक आहे;आणि 10.3125 Gbit/s बर्स्ट रिसेप्शन सेटअप वेळ <800ns असणे आवश्यक आहे आणि 10-3 च्या बिट त्रुटी दरासह बर्स्ट रिसेप्शन संवेदनशीलता <-28.0 dBm असणे आवश्यक आहे.

2.10G EPON सममितीय OLT ऑप्टिकल मॉड्यूल डिझाइन

2.1 डिझाइन योजना

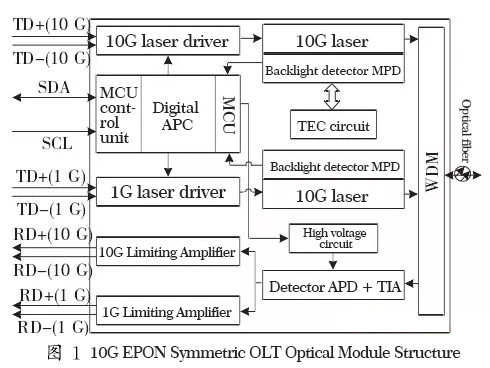

10G EPON सममितीय OLT ऑप्टिकल मॉड्यूल हे ट्रिपलेक्सर (सिंगल-फायबर थ्री-वे मॉड्यूल), ट्रान्समिटिंग, रिसीव्हिंग आणि मॉनिटरिंगचे बनलेले आहे.ट्रिपलक्सरमध्ये दोन लेसर आणि एक डिटेक्टर समाविष्ट आहे.प्रसारित प्रकाश आणि प्राप्त झालेला प्रकाश एकल-फायबर द्विदिशात्मक प्रसारण साध्य करण्यासाठी WDM (वेव्हलेंथ डिव्हिजन मल्टीप्लेक्सर) द्वारे ऑप्टिकल उपकरणामध्ये एकत्रित केले जातात.त्याची रचना आकृती 1 मध्ये दर्शविली आहे.

ट्रान्समिटिंग भागामध्ये दोन लेसर असतात, ज्यांचे मुख्य कार्य अनुक्रमे 1G आणि 10G इलेक्ट्रिकल सिग्नलला ऑप्टिकल सिग्नलमध्ये रूपांतरित करणे आणि डिजिटल APC सर्किटद्वारे बंद लूप स्थितीत ऑप्टिकल पॉवर स्थिरता राखणे आहे.त्याच वेळी, सिंगल-चिप मायक्रोकॉम्प्युटर सिस्टमला आवश्यक असलेले विलोपन गुणोत्तर प्राप्त करण्यासाठी मॉड्युलेशन करंटची परिमाण नियंत्रित करते.TEC सर्किट 10G ट्रान्समिटिंग सर्किटमध्ये जोडले गेले आहे, जे 10G लेसरच्या आउटपुट तरंगलांबीला मोठ्या प्रमाणात स्थिर करते.प्राप्त झालेला भाग APD चा वापर करून सापडलेल्या बर्स्ट ऑप्टिकल सिग्नलला इलेक्ट्रिकल सिग्नलमध्ये रूपांतरित करतो आणि प्रवर्धन आणि आकार दिल्यानंतर त्याचे आउटपुट करतो.संवेदनशीलता आदर्श श्रेणीपर्यंत पोहोचू शकते हे सुनिश्चित करण्यासाठी, वेगवेगळ्या तापमानांवर एपीडीला स्थिर उच्च दाब प्रदान करणे आवश्यक आहे.एपीडी हाय-व्होल्टेज सर्किट नियंत्रित करून एक-चिप संगणक हे लक्ष्य साध्य करतो.

2.2 ड्युअल-रेट बर्स्ट रिसेप्शनची अंमलबजावणी

10G EPON सममितीय OLT ऑप्टिकल मॉड्यूलचा प्राप्त करणारा भाग बर्स्ट प्राप्त करण्याची पद्धत वापरतो.त्याला 1.25 आणि 10.3125 Gbit/s च्या दोन भिन्न दरांचे बर्स्ट सिग्नल प्राप्त करणे आवश्यक आहे, ज्यासाठी प्राप्त करणारा भाग स्थिर आउटपुट इलेक्ट्रिकल सिग्नल प्राप्त करण्यासाठी या दोन भिन्न दरांचे ऑप्टिकल सिग्नल चांगल्या प्रकारे ओळखण्यास सक्षम असणे आवश्यक आहे.ओएलटी ऑप्टिकल मॉड्यूल्सचे ड्युअल-रेट बर्स्ट रिसेप्शन लागू करण्यासाठी दोन योजना येथे प्रस्तावित आहेत.

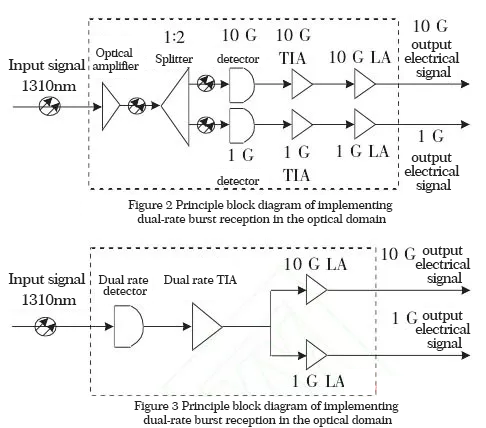

इनपुट ऑप्टिकल सिग्नल TDMA (टाईम डिव्हिजन मल्टिपल ऍक्सेस) तंत्रज्ञान वापरत असल्यामुळे, एकाच वेळी फक्त एकच प्रकाशाचा दर असू शकतो.इनपुट सिग्नलला 1:2 ऑप्टिकल स्प्लिटरद्वारे ऑप्टिकल डोमेनमध्ये वेगळे केले जाऊ शकते, जसे की आकृती 2 मध्ये दाखवले आहे. किंवा 1G आणि 10G ऑप्टिकल सिग्नलला कमकुवत इलेक्ट्रिकल सिग्नलमध्ये रूपांतरित करण्यासाठी फक्त हाय-स्पीड डिटेक्टर वापरा आणि नंतर दोन इलेक्ट्रिकल वेगळे करा. आकृती 3 मध्ये दर्शविल्याप्रमाणे, मोठ्या बँडविड्थ TIA द्वारे भिन्न दरांसह सिग्नल.

आकृती 2 मध्ये दर्शविलेली पहिली योजना 1: 2 ऑप्टिकल स्प्लिटरमधून प्रकाश जातो तेव्हा एक विशिष्ट अंतर्भूत नुकसान आणेल, ज्याने इनपुट ऑप्टिकल सिग्नल वाढवणे आवश्यक आहे, म्हणून ऑप्टिकल स्प्लिटरच्या समोर एक ऑप्टिकल अॅम्प्लीफायर स्थापित केला आहे.विभक्त ऑप्टिकल सिग्नल नंतर वेगवेगळ्या दरांच्या डिटेक्टरद्वारे ऑप्टिकल / इलेक्ट्रिकल रूपांतरणाच्या अधीन केले जातात आणि शेवटी दोन प्रकारचे स्थिर इलेक्ट्रिकल सिग्नल आउटपुट प्राप्त केले जातात.या सोल्यूशनचा सर्वात मोठा तोटा म्हणजे ऑप्टिकल अॅम्प्लिफायर आणि 1: 2 ऑप्टिकल स्प्लिटर वापरला जातो आणि ऑप्टिकल सिग्नलमध्ये रूपांतरित करण्यासाठी दोन डिटेक्टर आवश्यक असतात, ज्यामुळे अंमलबजावणीची जटिलता वाढते आणि खर्च वाढतो.

अंजीर मध्ये दर्शविलेल्या दुसऱ्या योजनेत.3, इलेक्ट्रिक डोमेनमध्ये पृथक्करण साध्य करण्यासाठी इनपुट ऑप्टिकल सिग्नलला फक्त डिटेक्टर आणि TIA मधून जाणे आवश्यक आहे.या उपायाचा गाभा TIA च्या निवडीमध्ये आहे, ज्यासाठी TIA ला 1 ~ 10Gbit/s ची बँडविड्थ असणे आवश्यक आहे आणि त्याच वेळी TIA ला या बँडविड्थमध्ये जलद प्रतिसाद आहे.केवळ TIA च्या वर्तमान पॅरामीटरद्वारे प्रतिसाद मूल्य त्वरीत मिळू शकते, प्राप्त संवेदनशीलता चांगली हमी दिली जाऊ शकते.हे समाधान अंमलबजावणीची जटिलता मोठ्या प्रमाणात कमी करते आणि खर्च नियंत्रणात ठेवते.वास्तविक डिझाइनमध्ये, आम्ही सामान्यतः दुहेरी-दर बर्स्ट रिसेप्शन प्राप्त करण्यासाठी दुसरी योजना निवडतो.

2.3 रिसीव्हिंग एंडवर हार्डवेअर सर्किटचे डिझाइन

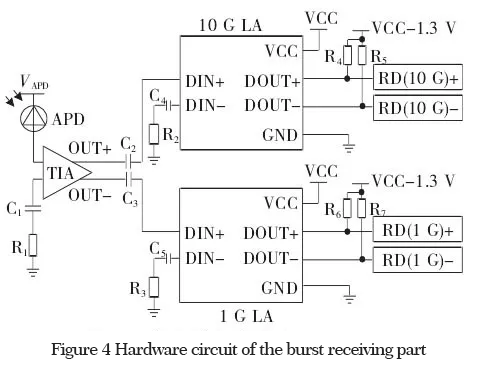

अंजीर 4 हे बर्स्ट रिसीव्हिंग पार्टचे हार्डवेअर सर्किट आहे.जेव्हा बर्स्ट ऑप्टिकल इनपुट असतो, तेव्हा APD ऑप्टिकल सिग्नलला कमकुवत इलेक्ट्रिकल सिग्नलमध्ये रूपांतरित करते आणि TIA कडे पाठवते.सिग्नलला TIA द्वारे 10G किंवा 1G इलेक्ट्रिकल सिग्नलमध्ये वाढवले जाते.10G इलेक्ट्रिकल सिग्नल हे TIA च्या पॉझिटिव्ह कपलिंगद्वारे 10G LA मध्ये इनपुट केले जाते आणि 1G इलेक्ट्रिकल सिग्नल TIA च्या नकारात्मक कपलिंगद्वारे 1G LA मध्ये इनपुट केले जाते.कॅपेसिटर C2 आणि C3 हे कपलिंग कॅपेसिटर आहेत जे 10G आणि 1G AC-कपल्ड आउटपुट प्राप्त करण्यासाठी वापरले जातात.AC-कपल्ड पद्धत निवडली गेली कारण ती DC-कपल्ड पद्धतीपेक्षा सोपी आहे.

तथापि, AC कपलिंगमध्ये कॅपेसिटरचा चार्ज आणि डिस्चार्ज असतो आणि सिग्नलला प्रतिसादाची गती चार्ज आणि डिस्चार्ज वेळेच्या स्थिरतेमुळे प्रभावित होते, म्हणजेच सिग्नलला वेळेत प्रतिसाद देता येत नाही.हे वैशिष्ट्य रिसेप्शन सेटलिंग वेळेची ठराविक रक्कम गमावण्यास बांधील आहे, म्हणून एसी कपलिंग कॅपेसिटर किती मोठे आहे हे निवडणे महत्वाचे आहे.एक लहान कपलिंग कॅपेसिटर निवडल्यास, सेटलिंगची वेळ कमी केली जाऊ शकते आणि प्रत्येक वेळेच्या स्लॉटमध्ये ओएनयूद्वारे प्रसारित होणारे सिग्नल रिसेप्शन प्रभावावर परिणाम न करता पूर्णपणे प्राप्त केले जाऊ शकतात कारण रिसेप्शन सेटलिंगची वेळ खूप मोठी आहे आणि पुढच्या वेळेस आगमन. स्लॉट

तथापि, खूप लहान कॅपेसिटन्स कपलिंग प्रभावावर परिणाम करेल आणि रिसेप्शनची स्थिरता मोठ्या प्रमाणात कमी करेल.मोठ्या कॅपॅसिटन्समुळे सिस्टीमचा त्रास कमी होऊ शकतो आणि रिसिव्हिंग एंडची संवेदनशीलता सुधारू शकते.म्हणून, रिसेप्शन सेटलिंग वेळ आणि रिसेप्शन संवेदनशीलता विचारात घेण्यासाठी, योग्य कपलिंग कॅपेसिटर C2 आणि C3 निवडणे आवश्यक आहे.याव्यतिरिक्त, इनपुट इलेक्ट्रिकल सिग्नलची स्थिरता सुनिश्चित करण्यासाठी, एक कपलिंग कॅपेसिटर आणि 50Ω च्या प्रतिकारासह जुळणारे प्रतिरोधक LA च्या नकारात्मक टर्मिनलशी जोडलेले आहेत.

LVPECL (लो व्होल्टेज पॉझिटिव्ह एमिटर कपलिंग लॉजिक) सर्किट R4 आणि R5 (R6 आणि R7) आणि 10G (1G) LA द्वारे विभेदक सिग्नल आउटपुटद्वारे 2.0 V DC व्होल्टेज स्त्रोतापासून बनलेले आहे.इलेक्ट्रिक सिग्नल.

2.4 लाँच विभाग

10G EPON सममितीय OLT ऑप्टिकल मॉड्यूलचा प्रसारित करणारा भाग प्रामुख्याने 1.25 आणि 10G ट्रान्समिटिंगच्या दोन भागांमध्ये विभागलेला आहे, जे अनुक्रमे 1490 आणि 1577 nm च्या तरंगलांबीसह डाउनलिंकला सिग्नल पाठवतात.उदाहरण म्हणून 10G ट्रान्समिटिंग भाग घेताना, 10G डिफरेंशियल सिग्नलची जोडी CDR (क्लॉक शेपिंग) चिपमध्ये प्रवेश करते, 10G ड्रायव्हर चिपशी AC-जोडलेली असते आणि शेवटी 10G लेसरमध्ये विभेदकपणे इनपुट केली जाते.कारण तापमानातील बदलाचा लेसर उत्सर्जन तरंगलांबीवर मोठा प्रभाव पडेल, तरंगलांबी प्रोटोकॉलला आवश्यक असलेल्या पातळीपर्यंत स्थिर करण्यासाठी (प्रोटोकॉलला 1575 ~ 1580nm आवश्यक आहे), TEC सर्किटचा कार्यरत प्रवाह समायोजित करणे आवश्यक आहे, त्यामुळे की आउटपुट तरंगलांबी चांगल्या प्रकारे नियंत्रित केली जाऊ शकते.

3. चाचणी परिणाम आणि विश्लेषण

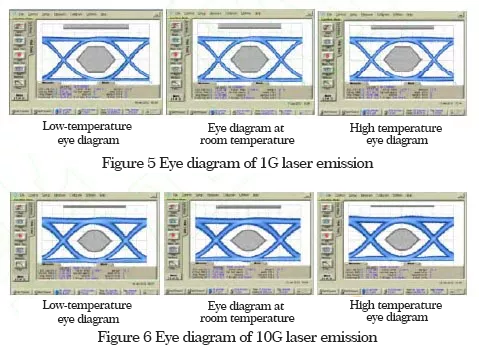

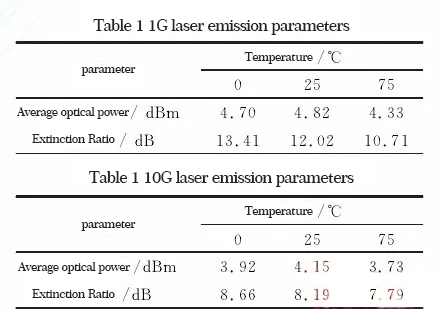

10G EPON सममितीय OLT ऑप्टिकल मॉड्यूलच्या मुख्य चाचणी निर्देशकांमध्ये रिसीव्हर सेटअप वेळ, रिसीव्हर संवेदनशीलता आणि ट्रान्समिट आय डायग्राम समाविष्ट आहे.विशिष्ट चाचण्या खालीलप्रमाणे आहेत:

(1) सेटअप वेळ प्राप्त करा

-24.0 dBm च्या अपलिंक बर्स्ट ऑप्टिकल पॉवरच्या सामान्य कार्य वातावरणात, बर्स्ट लाइट स्त्रोताद्वारे उत्सर्जित होणारा ऑप्टिकल सिग्नल मापन प्रारंभ बिंदू म्हणून वापरला जातो आणि मॉड्यूल मापन समाप्ती बिंदू म्हणून संपूर्ण विद्युत सिग्नल प्राप्त करतो आणि स्थापित करतो, त्याकडे दुर्लक्ष करून चाचणी फायबरमध्ये प्रकाशाचा वेळ विलंब. मोजलेली 1G बर्स्ट रिसेप्शन सेटअप वेळ 76.7 एनएस आहे, जी <400 एनएसच्या आंतरराष्ट्रीय मानकांची पूर्तता करते;10G बर्स्ट रिसेप्शन सेटअप वेळ 241.8 ns आहे, जो <800 ns च्या आंतरराष्ट्रीय मानकांना देखील पूर्ण करतो.

3. चाचणी परिणाम आणि विश्लेषण

10G EPON सममितीय OLT ऑप्टिकल मॉड्यूलच्या मुख्य चाचणी निर्देशकांमध्ये रिसीव्हर सेटअप वेळ, रिसीव्हर संवेदनशीलता आणि ट्रान्समिट आय डायग्राम समाविष्ट आहे.विशिष्ट चाचण्या खालीलप्रमाणे आहेत:

(1) सेटअप वेळ प्राप्त करा

-24.0 dBm च्या अपलिंक बर्स्ट ऑप्टिकल पॉवरच्या सामान्य कार्य वातावरणात, बर्स्ट लाइट स्त्रोताद्वारे उत्सर्जित होणारा ऑप्टिकल सिग्नल मापन प्रारंभ बिंदू म्हणून वापरला जातो आणि मॉड्यूल मापन समाप्ती बिंदू म्हणून संपूर्ण विद्युत सिग्नल प्राप्त करतो आणि स्थापित करतो, त्याकडे दुर्लक्ष करून चाचणी फायबरमध्ये प्रकाशाचा वेळ विलंब.मोजलेली 1G बर्स्ट रिसेप्शन सेटअप वेळ 76.7 एनएस आहे, जी <400 एनएसच्या आंतरराष्ट्रीय मानकांची पूर्तता करते;10G बर्स्ट रिसेप्शन सेटअप वेळ 241.8 ns आहे, जो <800 ns च्या आंतरराष्ट्रीय मानकांना देखील पूर्ण करतो.